|

|

今回は高周波回路基板に限定するものではなく一般的な高速回路などについてのノイズ対策事例をまず挙げたいと思います。

【LVDS信号の不適切な配線に起因する不要輻射について】

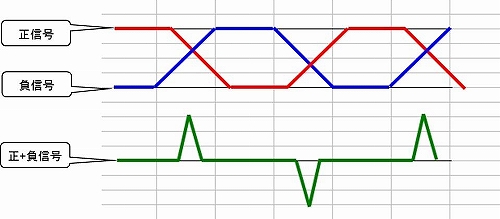

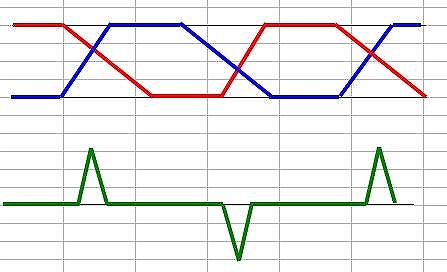

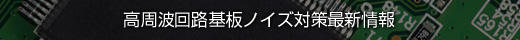

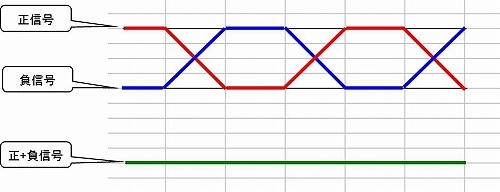

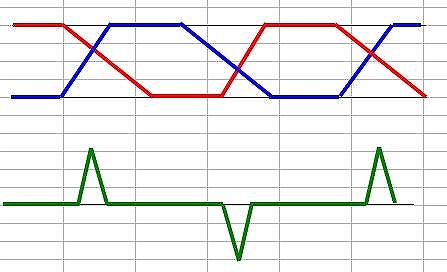

・基板上で発生する不要輻射の原因の一つとしてLVDS信号のタイミングのずれに起因するものが有ります。理想的なLVDS信号は正信号+負信号の合成波形は理論上0となり、これによって不要輻射に強い伝送線路となります。

ところが、何らかの原因でLVDSの正・負信号間での不整合が発生した場合クロスポイントが上下にばらつく事により合成波形に不要な電圧が発生し、これがLVDS信号上にコモンモード電流として流れ、大きな輻射ノイズを発生します。

このLVDS信号の不整合には色々な原因が有りますが、代表的なものに、「LVDS信号の不等長」があります。但しここで注意しなければならないのは「物理的な線長がイコールであれば信号の伝達速度がイコールになるわけではない」ということです。

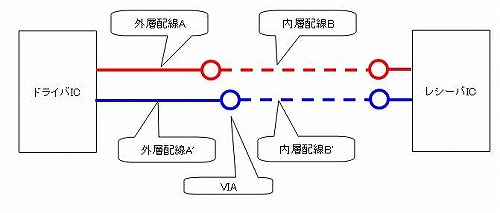

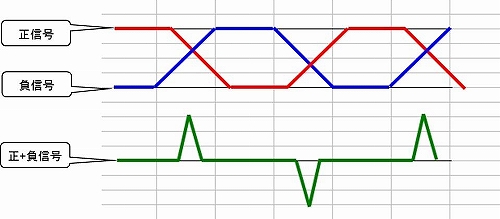

一例として上図の様なLVDS配線があったとします。

外層配線A+内層配線Bと外層配線A'+内層配線B'は物理的な配線長はイコールですが、AとA'、BとB'は配線長が異なります。ここで注意しなければならないのは「内層と外層では信号の伝達速度に違いがある」ということです。具体的には内層を走る信号の伝達速度は外層に比べて20〜30%程度遅くなるという現象が発生します(一般的なFR4の場合。使用材質メーカー等により変動します)。つまり上記の場合A+A'の信号はB+B'の信号よりも伝達時間が余計にかかるということになります。これにより、見た目上(物理的に)同じ配線長のLVDSの波形に不整合が生じる現象が発生します。LVDS信号を配線する場合は「物理配線長ではなく電気的な配線長を等しくする」必要があります。*同様なケースで、例えばクロック信号と同期をとるデータバス等の信号で、物理配線長は等しいが、クロック信号は全て内層、データバスは全て外層を使用して配線した場合、信号同期にズレが生じるケースがあります。また、稀なケースとして、低品質な(主にローコストの)LVDSドライバICの中にはON時とOFF時のスイッチング特性が異なるものが有ります。この様なケースでも正信号と負信号のクロスポイントが崩れ、不要輻射が発生します。こうなるともはや基板上で対策を施すのは不可能です。

この様に一見問題の無い様に見える伝送線路でも、基板の持つ特性、配線ルートの検証等、条件をトータルで満たさないと思わぬところで不具合が発生します。こういった複雑な配線ルートのスキューが条件を満たすかどうかの検証には、伝送線路シミュレーターが力を発揮します。

|

|

|

| |

|

|

|

|

|